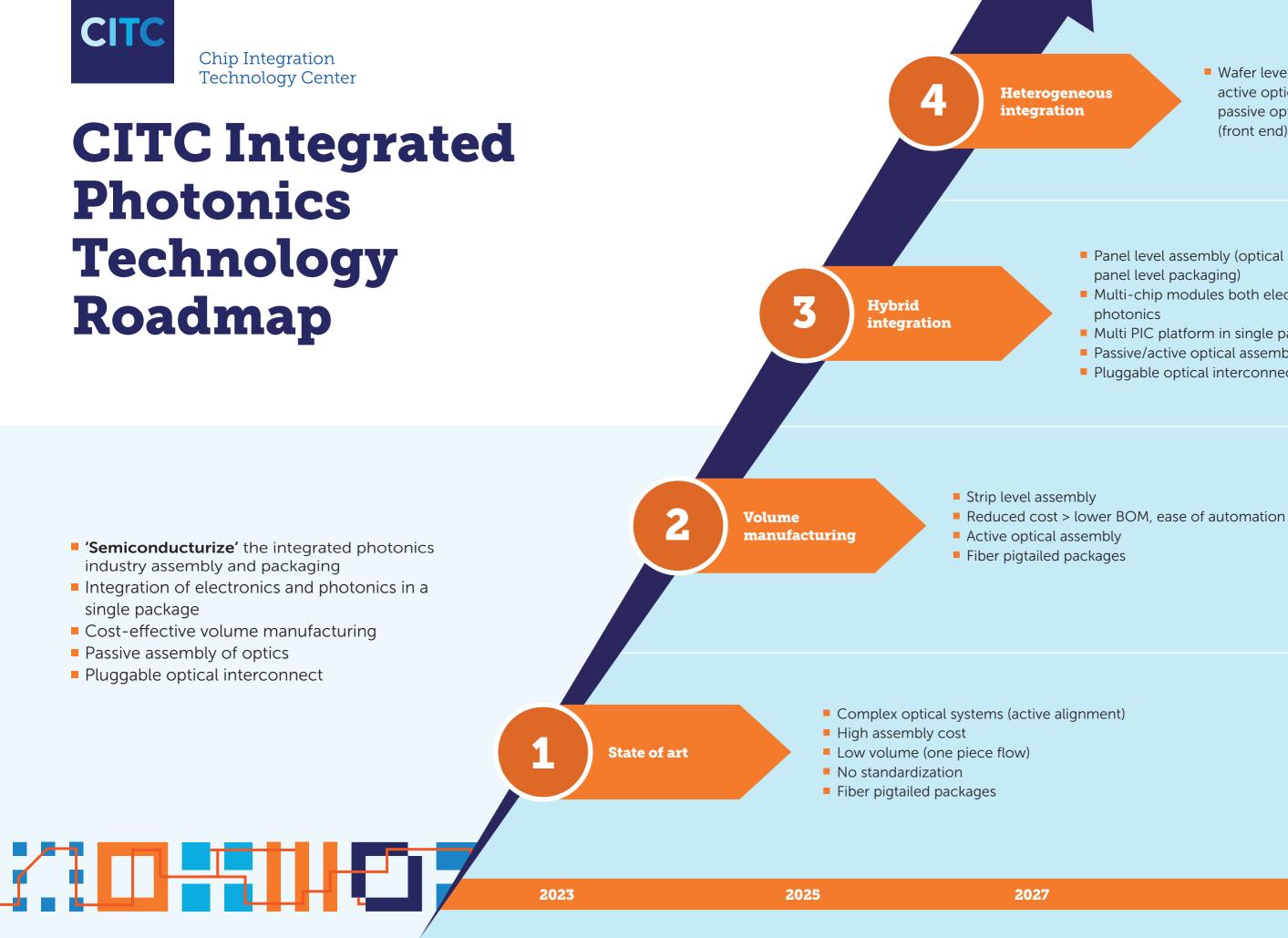

Wafer level integration of active optical material to passive optical structures (front end)

- Panel level assembly (optical fan out

- panel level packaging)

- Multi-chip modules both electronics and

- Multi PIC platform in single package

- Passive/active optical assembly of PIC

- Pluggable optical interconnect

## **Assembly and** packaging of integrated photonics today

#### Need

Start-up companies or established companies seek support in assembly and packaging of their (first) integrated photonic dies

#### **Activities**

- CITC supports these companies by sharing knowledge in electrical (RF) and optical packaging processes

- Design for processing criteria of the package

- Material and process selection for optical, electrical and thermal interconnect

- Develop process recipe and demonstration of process feasibility on limited amount of samples

Chip Integration echnology Center

# 'Semiconducturize' packaging of integrated photonics components

#### Need

- Scalable assembly and packaging for hybrid integration of semiconductor dies and integrated photonic dies

- Higher electrical and optical IO density

- Improved RF interconnect to increase bandwidth

- Improved thermal management

- Pluggable optics

### Result

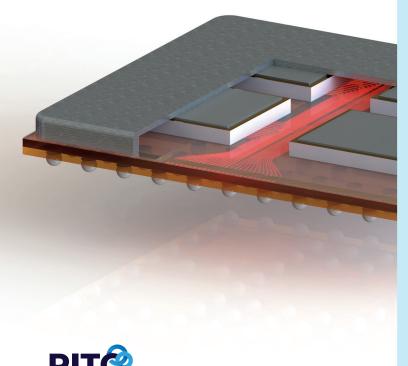

- CITC has defined a 'moon shot' package concept and processes for assembly and packaging of integrated photonic dies addressing the needs of upcoming photonic packaging

- The concept is a set of packaging technology building blocks for hybrid integration of semiconductor dies and integrated photonic dies in a single package

- The concept features chip to chip communication inside the package and outside world in both the optical and electrical domain

- In Dutch Growth Fund framework, CITC together with PITC develops and demonstrates the function of the technology building blocks

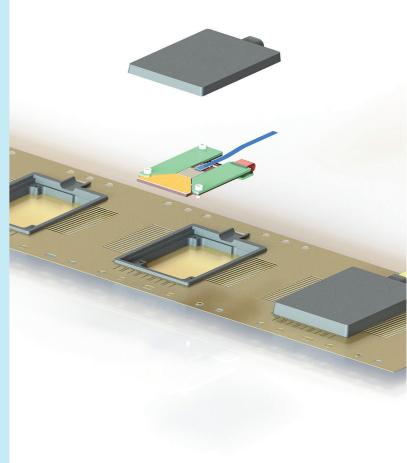

# Scalable manufacturing for integrated photonics packaging

### Need

- Assembly and packaging cost for integrated photonics is relatively high compared to semiconductor packaging

- Commonly used metal box package (butterfly package) is expensive and limits scaling of the assembly in volume

### Result

- Together with RJR technologies a lead frame with injection molded air-cavity packages has been developed as replacement for butterfly packages

- Using LCP material and solid metal base, the robust design provides near-hermetic performance (10<sup>-8</sup>)

- Strip format eases automation of assembly (automatic indexing and handling)

- Metal base features thermal expansion matched to minimize differential thermal stresses

- Cost efficient, roughly 50% cost reduction BOM

### Where our developments in semiconductors meet the challenges in integrated photonics

**Technologies in semiconductors**

Materials and technologies for 100 GHz and beyond

Die attach materials thermal conductivity >150 W/mK

Shared building blocks

Additive manufacturing technologies based on printing

> Strip/wafer and panel level concepts

**Challenges in integrated photonics**

Increased bandwidth

Better thermal performance

WLFOP increased electrical and optical IO density

Solutions for scalable volume manufacturing